Volume – 02, Issue – 09, September – 2017, PP – 47-50

# Low-Power High-Speed Circuit Design for VLSI Memory Systems under Recent Techniques

R. Purushotham Naik<sup>1</sup>, Dr.Sachin Saxena<sup>2</sup>

<sup>1</sup>Research Scholar, Department Of ECE Sun Rise University, Alwar, Rajasthan <sup>2</sup>Supervisor, Department of ECE Sun Rise University, Alwar, Rajasthan

**Abstract:** In current PC systems, different memory parts are utilized, for example, on-chip enlist documents, on-chip/off-chip reserve recollections, and off-chip primary recollections. High-speed memory framework design has been and will have been a standout amongst the most imperative issues. In microchips, for instance, the on-chip reserve sizes are developing with every era to connect the expanding disparity in the speeds of the processor and the principle memory. Power dissemination has likewise turned into a vital thought both because of the expanded reconciliation and working speeds, and in addition because of the unstable development of battery worked machines. In the theory, low-power high-speed circuits for recollections and processor-memory interface are researched.

To start with, anomalous spillage concealment (ALS) plan is proposed to repair standby current blunders in SRAMs because of gadget imperfections. By presenting spillage sensors, move registers and breakers the ALS faculties  $1\mu$ A of irregular spillage, detaches the memory cell deliberately from VDD lines and along these lines smothers strange spillage current. A 64Kbit test SRAM is created in 0.6µm CMOS innovation and the viability are illustrated. The range overhead reductions with the development of memory limit, and turn out to be under 1% for 4Mbit SRAMs, which guarantee the commonsense utilization of this plan in business applications.

Keywords: ALS, ISSCC, MTCMOS, VTCMOS, RRDV, PMOSRRDV, NMOSRRDV

## I. Introduction

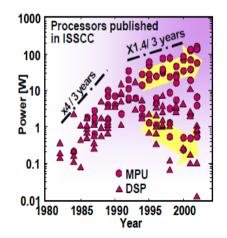

In modern computer systems, hierarchical memory architecture is widely used. There are various memory components inside one system, such as register files, cache memories, and main memories. High-speed memory system design has been and will have been one of the most important design issues. As systems go toward higher performance, capacity of these memories gets larger. In microprocessors, for example, on-chip cache sizes are growing with each generation to bridge the increasing divergence in the speeds of the processor and the main memory. Power dissipation has also become an important consideration both due to the increased integration and operating speeds, as well as due to the explosive growth of battery operated appliances. Figure 1.1 shows power trend of MPUs and DSPs presented at International Solid-State Circuits Conference (ISSCC) [1]. Power consumption of high-end processors is now over 100W. Today, low power is not only an issue for portable applications but also a stringent demand for high-speed applications.

Figure 1.1: Power trend of MPUs and DSPs presented ISSCC.

*Volume – 02, Issue – 09, September – 2017, PP – 47-50*

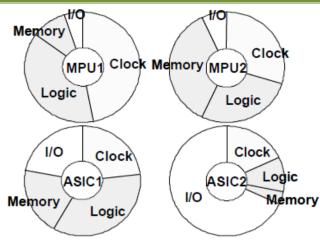

Figure 1.2: Power Distribution in CMOS LSIs.

Fig 1.1 shows several important parameters of future high-performance LSIs predicted by SIA [2]. In the year 2016, when the mainstream technology is shrunk down to 22nm gate length, the maximum on-chip clock frequency is 29GHz, microprocessor power is 288W with 0.5V supply voltage, and number of I/O pins is 7100. These goals cannot be reached by simply taking advantage of scaling scenario [3], since scaling of I/O related circuits is slower than that of core logic circuits. The main reasons lie in difficulties of packaging and also in special design considerations regarding me /Os such as ESD protection.

## **II.** Classification of Power Consumption

Though there are different types of power consumption, the major types that affect CMOS circuits are dynamic power and leakage power [1].

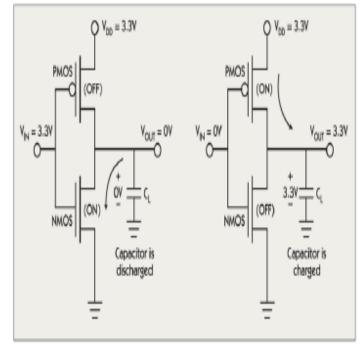

## 2.1. Dynamic power

Dynamic power [2] is the power that is consumed by a device when it is actively switching from one state to another [3]. Dynamic power consists of switching power consumed while charging and discharging the loads on a device, and internal power (also referred to as short circuit power), consumed internal to the device while it is changing state [4]. Fig. 1 shows the dynamic power dissipation that can occur in CMOS circuits.

*Volume* – 02, *Issue* – 09, *September* – 2017, *PP* – 47-50

#### **III. Adaptive Techniques**

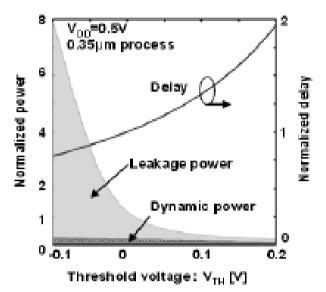

The power and the delay dependence on the threshold voltage at 0.5 VDD is shown in Fig. From Fig., it is inferred that to achieve high performance, Vth has to be decreased. But decreasing Vth could cause a significant increase in static leakage power component.

There are several approaches to reduce the stand by leakage current like MTCMOS (Multi Threshold CMOS) and VTCMOS (Variable Threshold CMOS) [11]. These schemes cannot suppress the active leakage power. Another approach is a dual threshold voltage approach, which is to partition a circuit into critical and non critical gates and use low *Vth* transistors only in the critical gates. The drawback of this scheme is that the leakage current cannot be sufficiently suppressed since the large leakage current always flows through the low *Vth* transistors.

## 1) Vth Hopping

Dynamic threshold voltage hopping scheme solves these problems [15]. This scheme utilizes dynamic adjustment of frequency and *Vth* through back gate bias control depending on the workload of the processor. When the workload is decreased, less power would be consumed by increasing *Vth* as depicted in Fig. This approach is similar to the dynamic *VDD* scaling, DVS. In the DVS scheme, voltage and frequency are controlled dynamically based on the workload variation.

#### **IV.** Conclusion

In this paper, circuit designs for future low-power high-speed memory systems are proposed. Fundamental memory circuit designs are explained especially on SRAMs and register files. Abnormal leakage suppression scheme is proposed to repair standby current errors in SRAMs. By introducing leakage sensors, shift registers and fuses the ALS senses  $1\mu$ A of abnormal leakage, isolates the memory cell systematically from VDD lines and thus suppresses abnormal leakage current. A 64Kbit test SRAM is fabricated in 0.6 $\mu$ m CMOS technology and the effectiveness are demonstrated. The area overhead decreases with the growth of memory capacity, and becomes less than 1% for 4Mbit SRAMs, which assures the practical use of the scheme.

Dual VDD and dual VTH memory designs including an SRAM and a register file is presented. High speed level-up converter using pseudo NMOS topology can reduce conversion delay to 50% of conventional circuits. A test chip integrating several level converters is designed in  $0.6\mu$ m CMOS technology and measured. The level converter is modified with replica adaptive bias circuits and implemented in a dual VDD SRAM and a register file. A test chip is fabricated in  $0.25\mu$ m triple- metal FD SOI CMOS technology. 2K-bit SRAMs and a 256-bit register file are integrated on a 16-bit microprocessor. The measured performance of the SRAM is 400MHz at 0.5/1.0V, 800MHz at 0.9V/1.8V, and 180MHz at 0.5V/0.5V supply voltage.

Fine-grain leakage control method is introduced and row-by-row dynamic VDD (RRDV) control scheme is proposed to suppress leakage power of dormant cells in an active mode. Cell leakage is reduced through DIBL effects when cell VDD of un-accessed rows is lowered to 0.2VDD, while bit- line leakage is reduced by applying negative voltage on inactive word lines. Measurement and simulation results indicate that

## International Journal of Latest Engineering Research and Applications (IJLERA) ISSN: 2455-7137

# *Volume* – 02, *Issue* – 09, *September* – 2017, *PP* – 47-50

the RRDV scheme can achieve 99.9% leakage reduction in scaled devices. The delay and area overhead of the RRDV scheme is estimated to be 5% and less than 7% respectively. Two variation of RRDV scheme, PMOS RRDV and NMOS RRDV are presented and their tradeoffs are discussed. PMOS RRDV controls cell data swing from VDD side while NMOS RRDV controls from VSS side. In terms of delay, area overhead, and noise margin, PMOS RRDV is superior to NMOS RRDV.

Sense amplifying cell (SAC) scheme to reduce 90% write power in wide SRAMs is also proposed in Chapter 5. SAC uses low-swing write technique with a 7-transistor cell. A test chip is fabricated in  $0.35\mu$ m CMOS technology and the effectiveness is demonstrated through measurements. It is pointed out that by combining SAC and NMOS RRDV scheme, reducing both leakage and write power is possible without using negative word line, which is great advantage of NMOS RRDV over PMOS RRDV.

A low-power yet high-speed memory-to-processor interface scheme, Wireless Super connects (WSC) scheme is proposed with the density of 625 pins/mm2. The interface utilizes capacitive coupled contact- less mini-pads, return-to- half-VDD signaling and sense amplifying F/F. The measured test chip in 0.35µm CMOS delivers up to 1.27 Gbps/pin with the power consumption of 3mW/pin. SPICE simulations with predicted 70nm transistor model shows that 7000 I/O's can be operate at 8.0GHz with only 1.63W.

## References

- Lossless Data Compression. Report Concerning Space Data System Standards, CCSDS 121.0 Blue Book. Issue 2. Washington, D.C. : CCSDS, May 2012.

- [2]. 2.Abhijit Jas, Jayabrata Ghosh-Dastidar, Mom-Eng Ng, and Nur A. Touba, An Efficient & quot; Test Vector Compression Scheme Using Selective Huffman Coding, & quot; IEEE in Trans. Compute.-Aided Des. Integer. Circuits Syst., vol. 22, no. 6, pp.797–806, Jun. 2003.

- [3]. 3. Y. Zorian, E. J. Marinissen, and system chips,"Proc.IEEEInt . Test in Conf., 1998, pp.130–143.

- [4]. 4. Chandra, and K. impression Chakravarty and Decompression for System-On-a-chip utilizing GolombVLSI co Test Symposium, pp. 113-120, 2000.

- [5]. 5. C.V. Krishna and N. A. Touba, & quote; LFSR Reseeding inside Processed. Of the Compress IEEE Global Test Conference (ITC), 2002.

- [6]. 6. F. F. Hsu, K. M. Head servant, and J execution of Illinois Proceedings of IEEE scanner Global Test Conference, 2001, pp. 538-547.

- [7]. 7. Hamzaogl and test application J.H time. For Patel, full " check embedded Proceeding scores of International Symposium on Fault-Tolerant Computing, 1999, pp. 260-267.

- [8]. 8. B. Koenemann et al., " A Smart Encoding,"Proc.10thAsian Test Symp. (ATS 01), IEEE CSPress, 2001, pp. 325-330.

- [9]. 9. M Ishida, D.Shaand T. Yamaguc for Compressing VLSI Test Symposium, Data & quot; pp.62-69, 1998.

- [10]. 10. M. Tehranipoora, M. Navneet, coded and K pressure method for testing embedded IEEE Core Trans.Very Large Scale Integer. Syst., vol. 10, no. 6, pp. 719–731, Jun.B. Chappell, FineArt"Theof IC Design," IEEE Spectrum,- 34. VO

- [11]. 11. Y.Bonhomme, et al., " Test control: a major issue in extensive SOC designs, & quote; in proceedings of the first IEEE Workshop on Electronics Design, Test and Applications, pp.447-449, 2002.

- [12]. 12. P.Parker, " Bare," in proceedings die test of IEEE Multi-Chip Module Conference, pp.24-27,1992. Study of Low power test data compression techniques for digital VLSI Circuits13

- [13]. 13. I.Polian, A.Czutro, S.Kundu, and B.Becker, International & quot; power conference on PC Design (ICCD' 06), PP-250, October 2006.243

- [14]. 14. H.Fai and N.Nicolici, & quote; Mechanized sweep chain divi-speed test," IEEE exchanges Aided Design of Integrated on Computer circuits and Systems,vol.27,no.11,pp.2092-2097,2008.

Author Details R.Purushotham Naik received M.Tech. in VLSI SYSTEM &DESIGN from JNTUH, and having 10 years of experience in teaching currently pursuing Ph.D in sun rise university ,Alwar,Rajasthan,